### Intel<sup>®</sup> StrongARM<sup>®</sup> SA-1111 Microprocessor Development Module

**User's Guide**

**ADVANCE INFORMATION**

January 2000

Phase 4

**Notice:** This document contains information on products in the sampling and initial production phases of development. Revised information will be published when this product is available.

Order No: 278281-003

Information in this document is provided in connection with Intel products. No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted by this document. Except as provided in Intel's Terms and Conditions of Sale for such products, Intel assumes no liability whatsoever, and Intel disclaims any express or implied warranty, relating to sale and/or use of Intel products including liability or warranties relating to fitness for a particular purpose, merchantability, or infringement of any patent, copyright or other intellectual property right. Intel products are not intended for use in medical, life saving, or life sustaining applications.

Intel may make changes to specifications and product descriptions at any time, without notice.

Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order.

Copies of documents which have an ordering number and are referenced in this document, or other Intel literature may be obtained by calling 1-800-548-4725 or by visiting Intel's website at http://www.intel.com.

Copyright © Intel Corporation, 2000

$\ensuremath{^{\star}}\xspace \xspace \xspace \xspace$  Other brands and names are the property of their respective owners.

ARM and StrongARM are trademarks of ARM, Ltd.

# int<sub>el</sub>。 Contents

| 1       | Intro                                                                       | duction                                                                                                                                                                                                                                                                                                                                                                                                                                            | 1–1                                     |

|---------|-----------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|

|         | 1.1<br>1.2                                                                  | Related DocumentationSA-1110 Development Platform Overview                                                                                                                                                                                                                                                                                                                                                                                         |                                         |

| 2       | Getti                                                                       | ng Started                                                                                                                                                                                                                                                                                                                                                                                                                                         | 2–1                                     |

|         | 2.1                                                                         | Unpacking the Intel® StrongARM® SA-1111 Development Module  2.1.1 Intel® StrongARM® SA-1111 Development Module Software  Hardware Installation                                                                                                                                                                                                                                                                                                     | 2–4<br>2–4<br>2–4                       |

| 3       | Theo                                                                        | ory of Operation                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                         |

|         | 3.1                                                                         | SA-1111 Block Diagram                                                                                                                                                                                                                                                                                                                                                                                                                              | 3–3<br>3–3<br>3–4                       |

| 4       | Hard                                                                        | ware Considerations                                                                                                                                                                                                                                                                                                                                                                                                                                | 4–1                                     |

|         | 4.1<br>4.2<br>4.3<br>4.4<br>4.5<br>4.6<br>4.7<br>4.8<br>4.9<br>4.10<br>4.11 | General-Purpose Expansion Bus Headers Expansion Flash Memory General-purpose Status Input Switch and Jumper Descriptions CPLD Register Map Interrupt Reason Register SDRAM 4.6.1 Expansion SDRAM Interface PCMCIA and Compact Flash USB Host PS/2 Port RS-232 Ports Debug CPLD 4.11.1 Modem Control 4.11.2 4x4 Debug Keypad 4.11.3 LEDs 4.11.4 Audio SPI Port Ethernet Interface Power Measurement Analog Outputs 4.15.1 Board Identification Bits | 4-14-24-34-44-54-64-64-74-94-104-124-12 |

| Α       | CPLI                                                                        | D Code                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                         |

| •       | A.1                                                                         | SA11MOD1.PHD File Contents                                                                                                                                                                                                                                                                                                                                                                                                                         |                                         |

| Figures |                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                         |

|         | 1-1<br>1-2<br>2-1                                                           | Preliminary Intel® StrongARM® SA-1110 Developer Platform  Preliminary Cross-Sectional view of SA-1110 Development Platform  SA-1111 Development Module (Side 1)                                                                                                                                                                                                                                                                                    | 1–3                                     |

### intel<sub>®</sub>

|               | 2-2  | SA-1111 Development Module (Side 2)                         | 2-3  |

|---------------|------|-------------------------------------------------------------|------|

|               | 2-3  | Master Power Clip Location on the SA-1110 Development Board |      |

|               | 2-4  | Aligning Connectors                                         |      |

|               | 2-5  | Connecting the Modules-Top View                             | 2–6  |

|               | 2-6  | Connecting the Modules–Side View                            |      |

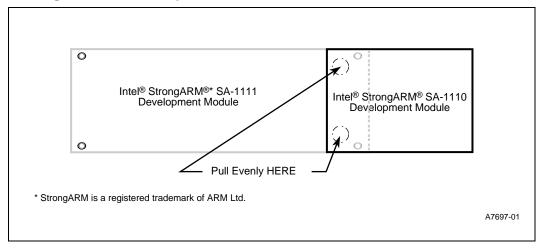

|               | 2-7  | Pulling the Connectors Apart                                |      |

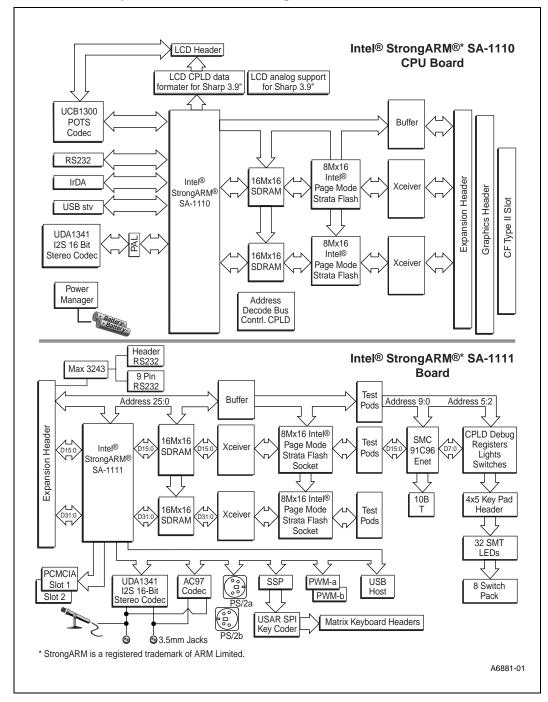

|               | 3-1  | SA-1110 Development Platform Block Diagram                  |      |

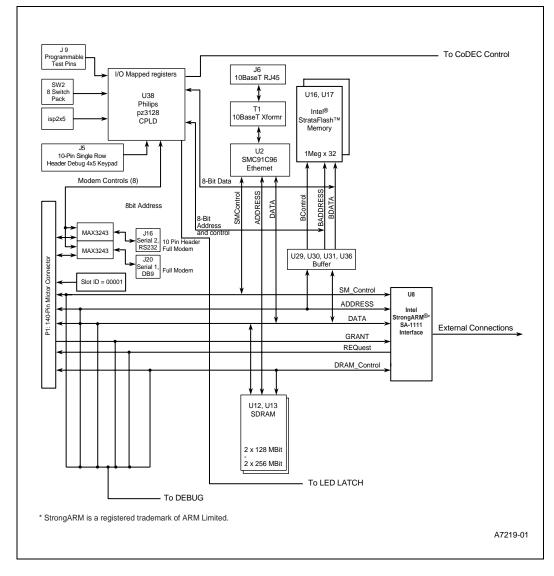

|               | 3-2  | On-board Support Signals                                    |      |

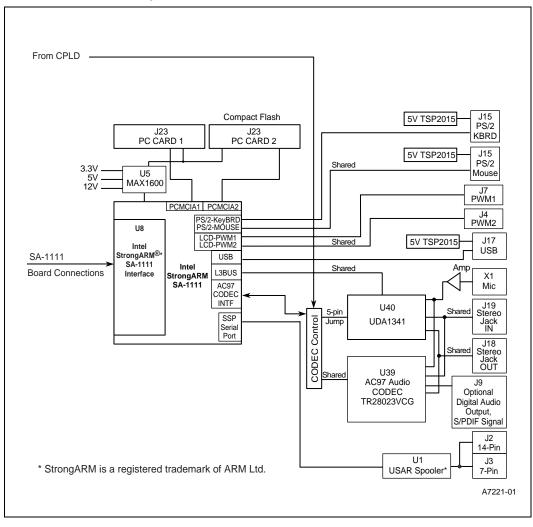

|               | 3-3  | Audio and External Inputs                                   |      |

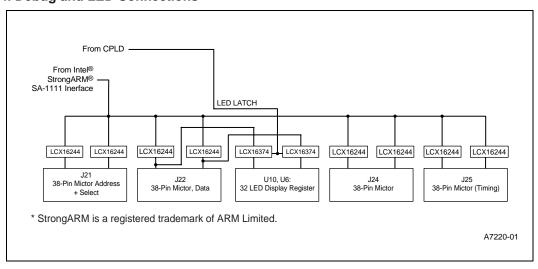

|               | 3-4  | Debug and LED Connections                                   |      |

| <b>Tables</b> |      |                                                             |      |

|               | 3-1  | Logic Analyzer Pin Assignments                              | 3–6  |

|               | 4-1  | Bank 0 Location                                             | 4–1  |

|               | 4-2  | Switch and Jumper Descriptions                              | 4–2  |

|               | 4-3  | Register Descriptions                                       | 4–3  |

|               | 4-4  | Interrupt Reason Register 10000024                          | 4–4  |

|               | 4-5  | Bank Selection Jumpers                                      | 4-5  |

|               | 4-6  | Control Register0 NCR_0 0x1000,00A0                         | 4–7  |

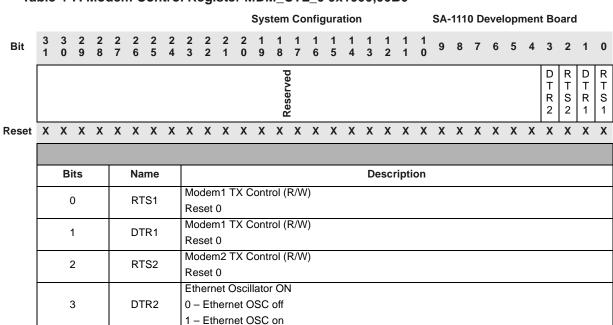

|               | 4-7  | Modem Control Register MDM_CTL_0 0x1000,00B0                | 4–8  |

|               | 4-8  | Modem Control Register MDM_CTL_0 0x1000,00B0                | 4–8  |

|               | 4-9  | Debug Keypad Description                                    | 4–9  |

|               | 4-10 | LED Mapping                                                 | 4–9  |

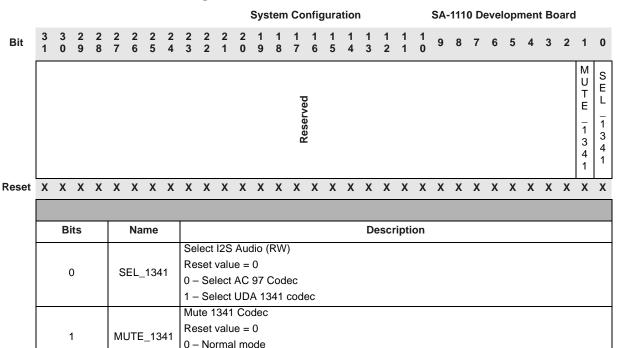

|               | 4-11 | Audio Control Register AUD_CTL 0x1000,00C0                  | 4-10 |

|               | 4-12 | Ethernet LED Indicators                                     | 4–11 |

|               | 4-13 | Ethernet Interface Signals                                  | 4–11 |

|               | 1-11 | Test Hooks                                                  | 1_12 |

# Introduction 1

The Intel® StrongARM® SA-1111 Microprocessor Companion Chip (SA-1111) is a companion chip to the SA-1110, providing a variety of functions suitable for use in a high-performance handheld computer system. The SA-1111 brings a new level of integration to small systems, providing a variety of I/O functions that enable complete systems to be built with very little "glue" logic. In addition to a complete USB Host Controller, the SA-1111 includes extensive support for PCMCIA and Compact Flash (CF), two PS/2 ports, two industry-standard serial ports, and other I/O capabilities. It can acquire the system memory bus and do DMA transfers to system memory (SDRAM) with its high-performance memory controller. For more information about the SA-1111 device, see the Intel®StrongARM® SA-1111 Companion Chip Developer's Manual, order number 278242.

The Intel<sup>®</sup> StrongARM<sup>®</sup> SA-1110 Microprocessor (SA-1110) is a highly integrated communications microcontroller that incorporates a 32-bit StrongARM<sup>®</sup> RISC processor core, system support logic, multiple communication channels, an LCD controller, a memory and PCMCIA controller, and general-purpose I/O ports. For more information about the SA-1110 device, see the Intel<sup>®</sup> StrongARM<sup>®</sup> SA-1110 Microprocessor Advanced Developer's Manual, order number 278240.

The Intel<sup>®</sup> StrongARM<sup>®</sup> SA-1110 Development Platform (SA-1110 Development Platform) is based upon these devices and is composed of a three board set:

- Intel<sup>®</sup> StrongARM<sup>®</sup> SA-1110 Development Board<sup>1</sup> (SA-1110 Development Board) order number SA1110DEVBD.

- Intel<sup>®</sup> StrongARM<sup>®</sup> SA-1111 Companion Chip Development module (SA-1111 development module) order number SA1111DEVMOD.

- Graphics accelerator board (available from third party vendors)

The SA-1110 Development Platform has many purposes:

- Hand held applications development and reference design

- Windows CE applications development platform

- · General OS applications development platform

- RF communications development platform

**Note:** This document and module are for Phase 4 of this product. For the latest information and updates, see the hardware release notes that are provided in hardcopy format, and the software readme.txt files that are provided in the software kits.

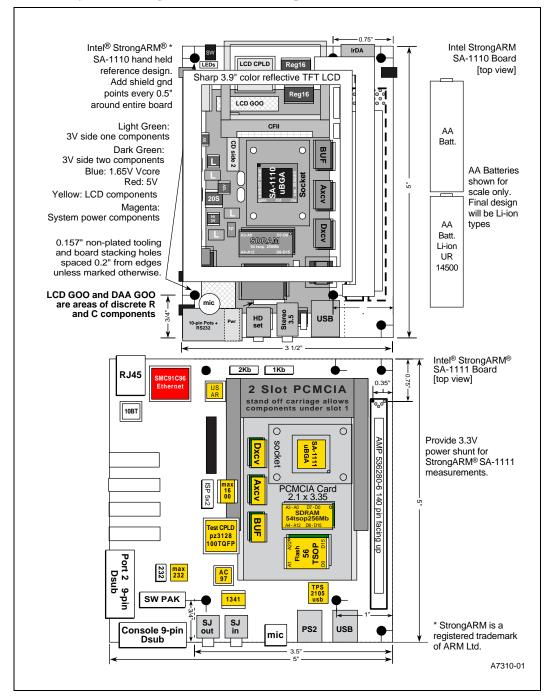

Figure 1-1 shows the preliminary front view of the SA-1110 Development Platform and Figure 1-2 shows a preliminary cross-sectional view.

For more information about the SA-1110 Development Board, see the Intel<sup>®</sup> StrongARM<sup>®</sup> SA-1110 Microprocessor Development Board User's Guide.

Figure 1-1. Preliminary Intel® StrongARM® SA-1110 Developer Platform

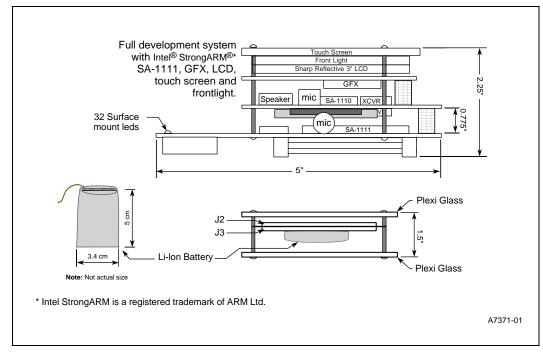

Figure 1-2 shows a preliminary sideview of the SA-1110 development board:

Figure 1-2. Preliminary Cross-Sectional view of SA-1110 Development Platform

The modular design of the SA-1110 Development Platform makes it a flexible, extendable and reusable design that supports<sup>1</sup> the following requirements:

- Targeted for hand-held applications

- Multiple OS development platform

- Third-party vendor graphics accelerator development platform

- Development platform for SA-1111 Companion Chip

- SA-1110 Development Board may be used as a palm PC reference design and development platform.

- SA-1110 Development Board may be used as host board for PCI bridge ASIC/FPGA and a Windows CE reference platform

- Battery powered design example

- Power management and battery management including SMBus and SBS development platform

- RF communications development board with interfaces for CDMA and GSM and Bluetooth<sup>2</sup> RF modules

<sup>1.</sup> The SA-1110 Development Platform has not been certified as being compliant with FCC, CE, UC, or PTT telephone standards or regulations.

<sup>2.</sup> For the phase 1 release of this document, formal Bluetooth interface specifications were not available. For more information, see section Section 4.13.3.

#### 1.1 Related Documentation

Other documentation that may be helpful while reading this document are described in the following table:

| Title                                                                                                                       | Location                                                         |  |  |  |

|-----------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------|--|--|--|

| Intel® StrongARM® SA-1110 Microprocessor Advanced Developer's Manual, order number: 278240                                  |                                                                  |  |  |  |

| Intel <sup>®</sup> StrongARM <sup>®</sup> SA-1110 Microprocessor Specification Update, order number: 278259                 |                                                                  |  |  |  |

| Intel® StrongARM® SA-1110 Development Board Parts List, order number: 278280                                                |                                                                  |  |  |  |

| Intel® StrongARM® SA-1110 Development Board User's Guide, order number: 278278                                              |                                                                  |  |  |  |

| Intel® StrongARM® SA-1110 Development Board Schematics, order number: 278279                                                | Intel's website for developers is at: http://developer.intel.com |  |  |  |

| Intel <sup>®</sup> StrongARM <sup>®</sup> SA-1111 Microprocessor Companion Chip<br>Developer's Manual, order number: 278242 |                                                                  |  |  |  |

| Intel® StrongARM® SA-1111 Microprocessor Companion Chip<br>Specification Update, order number: 278260                       |                                                                  |  |  |  |

| Intel® StrongARM® SA-1111 Companion Chip Development Board Schematics, order number: 289282                                 |                                                                  |  |  |  |

| Intel® StrongARM® SA-1111 Companion Chip Development Board Parts List, order number: 278283                                 |                                                                  |  |  |  |

| The ARM Debug Monitor: Angel                                                                                                | ARM's website is at:                                             |  |  |  |

| ARM Architecture Reference Manual                                                                                           | http://www.arm.com                                               |  |  |  |

#### 1.2 SA-1110 Development Platform Overview

The SA-1110 Development Board, the SA-1111 Development Module, and the graphics accelerator boards are designed to be a flexible software and hardware development environment and example design. When the SA-1110 Development Board is used as a development system, the SA-1111 Development Module is also required to provide Ethernet, serial port, LEDs and logic analyzer support.

The SA-1110 Development Board has the following resources and features:

- Up to 32MB socketed fast page mode Intel<sup>®</sup> StrataFlash<sup>TM</sup> memory

- Up to 64MB 100 MHz SDRAM

- Un-buffered main memory interface allows highest possible SDRAM memory bandwidth

- Small form factor 3.5" x 5" x 0.5" (same size as the Nino\*)

- UCB1300 codec supports microphone, speaker, POTS line soft modem DAA connections and touch screen

- UDA1341 stereo codec supports high quality 16 bit stereo audio record and playback

- Infra-red interface for IrDA data links up to 4Mb

- Battery powered, using high efficiency DC-DC converters and a single Lithium ion (Li-ion) cell

- Smart battery technology development platform and reference design when used with smart battery packs

- Integrated 3.9" reflective color TFT LCD and touch screen

- Optional 8" color passive LCD for use with GFX companion chip

- Two expansion headers for the SA-1111 Development Module, the graphics accelerator board, or other boards

- Built in mini speaker and two microphones

- Built in quiet alert vibration motor

- One type II Compact Flash socket (available only when the SA-1111 Development Module and graphics accelerator boards are not present)

- USB slave port for PC synchronization and battery trickle charge

- RF module interface connector for CDMA, GSM and Bluetooth modules up to 4 Watts

- Base station connector for JTAG programming, RS232, power input, and telephone

#### The SA-1111 Development Module has the following features<sup>1</sup>:

- Expansion Flash bank. Up to 32MB socketed fast page mode StrataFlash memory

- Expansion SDRAM bank (up to 64MB 50MHz SDRAM)

- Supports UDA1341 stereo codec for high quality 16 bit stereo audio record and playback

- Supports AC97 stereo codec for high quality 16 bit stereo audio record and playback

- Form factor is six inches by five inches by 1.38 inches

- Built in microphone

- One type II PCMCIA socket (inner slot)

- One type II Compact Flash socket (outer slot)

- USB host port

- · USB host plug and power control device

- PS\2 port for mouse and trackpad

- Logic analyzer pods

- 32 LEDs to display program debug data

- 10BASE-T Ethernet controller

- Two debug serial ports (RS-232)

For more information about the SA-1111 Development Module, see the Intel<sup>®</sup> StrongARM<sup>®</sup> SA-1111 Companion Chip Development Module User's Guide.

#### Introduction

The graphics accelerator board has the following features<sup>1</sup>:

- Third-party high performance graphics accelerator

- Two head display support; Analog XGA and LCD XGA

- Direct connection for Sharp LM8V31 dual scan STN VGA color panel with backlight and touch screen

<sup>1.</sup> For more information about the graphics accelerator board, see the third-party documentation.

# Getting Started

2

This SA-1111 Development Module is supplied as a daughter card, which is an optional development module for the SA-1110 Development Board. This chapter provides a physical description of the SA-1111 Development Module and describes how to:

- Unpack the cards and give them a visual inspection

- Install required hardware

- · Install required software

- Select the various card modes

- Configure the card to suit your application

- Power-up the cards for the first time

#### 2.1 Physical Description

Figure 2-1 shows the physical layout of the SA-1111 Development Module. The SA-1111 Development Module is a 10-layer double-sided board with surface mount assembly technology. The SA-1111 Development Module contains the SA-1111 companion chip, expansion flash, expansion SDRAM, audio codecs, various serial I/O connections, PCMCIA and Compact Flash support, an in-circuit programmable CPLD pre-programmed for control and additional debug capability, and an interface to the SA-1110 Development Board. The default setting for switches and jumpers are defined in Table 4-2.

The following are debug specific features which are isolated from the rest of the board:

- Nine-pin DB9 RS-232 communications port connector with full modem support for system debug and software development.

- Ten-pin header RS-232 second communications port with full modem support that can be used for hardware flow control or for passing debug messages from the development environment.

- Ethernet Controller SMC LAN91C96 for development environment communications.

- 32 LEDs for user-defined status and system debug display.

- Four buffered 38-pin Mictor logic analyzer connectors.

- 32 LEDs for status display

Figure 2-1. SA-1111 Development Module (Side 1)

Figure 2-2. SA-1111 Development Module (Side 2)

# 2.1 Unpacking the Intel<sup>®</sup> StrongARM<sup>®</sup> SA-1111 Development Module

**Caution:** This board contains electronic components that are susceptible to permanent damage from electrostatic discharge (static electricity). To prevent electrostatic discharge, it is supplied in an

antistatic bag. When handling the board, risk of damage can be alleviated by following a few simple precautions:

- Remove the board from the bag only when you are working on an antistatic, earthed surface and wearing an earthed antistatic wrist strap.

- Keep the antistatic bag that the card was supplied in; if you remove the board from a system, store it back in the bag.

- Do not touch the gold contacts.

#### 2.1.1 Intel<sup>®</sup> StrongARM<sup>®</sup> SA-1111 Development Module Software

To purchase an ARM Software Development Kit (SDT), see your Intel sales representative.

The following source and executable files are available from the StrongARM section in the developer's area on the Intel website.

- Sample source code including I/O drivers such as the software video-processing engine drivers and the SCB library available through Intel's developer's web site.

- Angel boot loader—Software component of ARM that loads an application from a remote host computer or from the application flash

- Set of microHAL libraries (to be used with Angel)—Set of drivers for communicating with the SA-1100 multimedia development board

- Diagnostics---Test program that analyze the functions of the SA-1110 Development Board.

Note: All software is available from the StrongARM section in the developer's area on the Intel website.

#### 2.2 Hardware Installation

After unpacking and inspecting the contents of the SA-1111 Development Module and the SA-1110 Development Board packages, the SA-1111 Development Module must be mounted to the SA-1110 Development Board.

Caution:

The 140-pin connectors are very fragile on the SA-1110 Development Board and the SA-1111 Development Module. Care must be taken when assembling these modules. If the 140-pin connector is damaged due to an improper assembly, the module(s) must be replaced.

#### 2.2.1 Connecting and Disconnecting the Modules

This section describes how to connect and disconnect the modules.

Note:

The following procedure assembles the SA-1110 Development Platform providing easy access to components and test points. The SA-1110 Development Platform can also be assembled in a

compact form factor as shown in Figure 1-2. The same method is used for either installation except that the SA-1110 Development Board is inverted for compactness.

1. On the SA-1110 Development Board, verify that the jumper (shunt) for J22 is **not** on the Master Power Clip (J22 should appear as two bare pins).

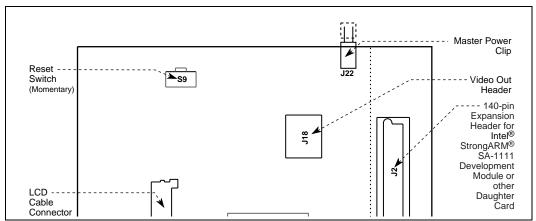

Figure 2-3. Master Power Clip Location on the SA-1110 Development Board

Verify that the Compact Flash adapter card has been installed in the inner slot of the PCMCIA socket J23B.

Note: Because of the extreme low power requirements, special precautions for airflow are not required.

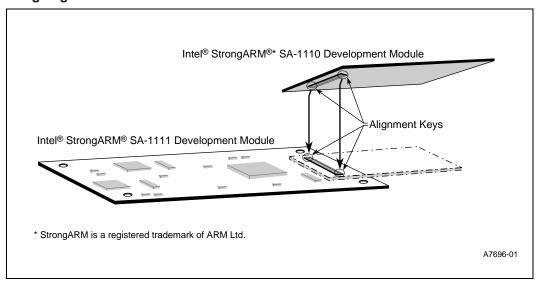

3. Align the keys of the 140-pin AMP expansion connector P1 on the SA-1111 Development Module to the mating expansion connector on the SA-1110 Development Board at the board edges as shown in Figure 2-4.

Figure 2-4. Aligning Connectors

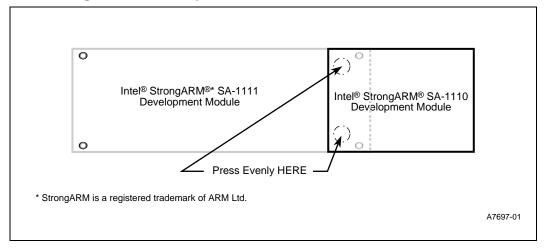

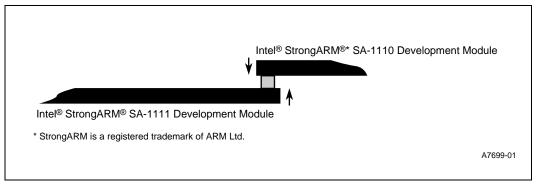

4. Nearest the board edges, gently press together and install the mounting hardware as shown in Figure 2-5 and Figure 2-6. Slide the connector in until it is firmly seated.

*Note:* The opposite facing second expansion connector on the SA-1110 Development Board can be used by an optional third-party graphics module.

Figure 2-5. Connecting the Modules-Top View

Figure 2-6. Connecting the Modules-Side View

5. To remove the SA-1111 Development Module, evenly pull the modules apart as shown in Figure 2-7.

*Note:* Twisting the modules apart or applying uneven pressure can damage the connectors.

Figure 2-7. Pulling the Connectors Apart

#### 2.2.2 **Power**

The SA-1111 Development Module uses a small form factor that resembles a Palm-size PC and draws power from the 140 pin connector (see sheet 3 of 11).

For information about how to power up the SA-1110 Development Platform and for information about LI-Ion (Li-Ion) batteries and battery management circuitry, see the *Intel*<sup>®</sup> *StrongARM*<sup>®</sup> *SA-1110 Development Board User's Guide*.

## Theory of Operation

3

The SA-1110 Development Platform has been designed for the hardware and software development of hand held, palm top and tethered applications. The SA-1110 Development Platform provides all of the system components necessary for a Windows CE\* sub-notebook system development platform with three independent video heads and high quality stereo sound.

The SA-1111 Development Module supplements the SA-1110 Development Platform by providing a vehicle to evaluate the SA-1111 Companion Chip, expanding the SA-1110 development environment, and providing general system debug features.

The SA-1111 improves the hardware and software developer's environment by supporting the following components:

- Ethernet 10BaseT port (RJ45 connector)

- Four logic analyzer connectors (Hewlett-Packard and Tektronix compatible 38-pin Mictors)

- Two debug serial ports with full modem capability

- LED display

- · Keypad and matrix keypad I/O

- PS/2 ports with power control

- Expansion SDRAM memory (64 MB, 50 MHz)

- Socketed, buffered expansion Flash memory (32 MB Intel Strataflash<sup>TM</sup>

- One each Type II/III PCMCIA socket and Compact Flash socket with power control

- Philips UDA1341 and AC97 codecs sharing the microphone, input, and output jacks

- Access to two PWM signals from the SA-1111 companion chip

- USB host connector with power control

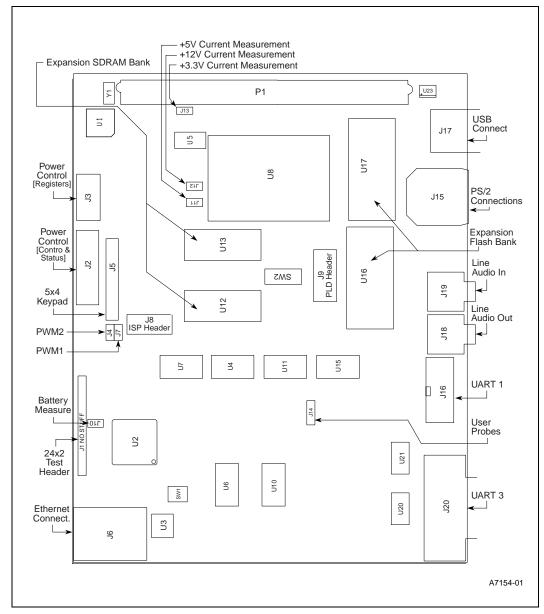

Figure 3-1. SA-1110 Development Platform Block Diagram

The block diagram shown in Figure 3-1 illustrates the modularity, flexibility and extend ability of the design. The SA-1110 Development Board supports two 140 pin fully buffered daughter board expansion headers. One of these expansion headers is for the SA-1111 Development Module, the other is for a graphics accelerator board.

The system partitioning is intended to allow the SA-1110 Development Board to be a minimal palm PC system. All device interfacing is implemented with in-system programmable CPLDs and most system interface points are available on connectors suitable for daughter boards or cables. Although not intended as a ready to manufacture product design, the SA-1110 Development Platform provides the basis for low-cost derivative designs.

#### 3.1 SA-1111 Block Diagram

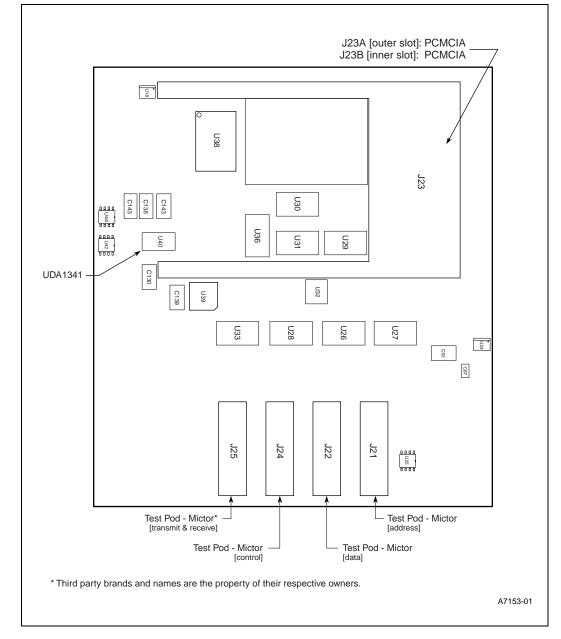

The SA-1111 Development Module supports a variety of on board audio peripherals, expansion memory, serial I/O connectivity, support signals such as memory, Ethernet, modems, switches, CPLD control, PCMCIA and Compact Flash sockets, (see Figure 3-2 and Figure 3-3), and external stimuli such as sound, keyboard input, mouse, debugging connections and indicators (see Figure 3-4).

#### 3.1.1 Expansion Connector Interface

Figure 3-2 shows the expansion connector interface from the SA-1110 Development Board to the SA-1111 Development Module. The SA-1110 control signals from serial channels 1 and 3 are also made available on the expansion connector to implement two RS-232 serial ports on the SA-1111 Development Module. These serial ports are application dependent, but are primarily intended for in passing messages in the debug environment. Serial port 2 at J16 can be used to support a PC-type keyboard, since the +12 V keyboard power can be optionally supplied to the connector. In addition to supporting system I/O mapped registers, an in system programmable CPLD is used to interpret an 8-position switch pack, providing modem control signals to the RS-232 debug ports, control switching between 1 of 2 on-board audio codecs, and interface to a 4x5 keypad used for debug purposes. The unused CPLD pins are brought out to a header for user access. Expansion SDRAM and socketed Flash memory can be accessed by either the SA-1110 or SA-1111 device. An Ethernet controller and 10BaseT interface are provided for communications in software development environments.

Figure 3-2. On-board Support Signals

#### 3.1.2 Serial Connectivity

Figure 3-3 shows the SA-1111 Development Module's serial connectivity. A PS/2 serial port and a USB host port are supported by the SA-1111 device. The SA-1111 Development Module provides power control for each of these ports. Two PWM signals from the SA-1111 device are available for possible applications in LCD brightness and contrast control.

The SA-1111 Development Module contains two audio codec devices. The Philips UDA1341 is I<sup>2</sup>S compatible and interfaces to the SA-1111 L3 bus. An AC 97 codec is also available that connects to the AC-Link interface and shares the SA-1111 Development Module's microphone and audio jacks, as well as the serial data paths between the SA-1111 and the codecs. Since only one

audio codec can be active at a time, some external logic controlled by the SA-1111 Development Module's CPLD determines device selection. Optionally, installing an AC97 device at U39 with digital audio output signal S/PDIF at pin 48, allows for that signal to be present at header J9.

The SSP serial port block on the SA-1111 device is connected to a USAR SPIcoder\* device that interfaces to an 8x14 matrix keyboard. Also shown in Figure 3-3 are the SA-1111 PCMCIA and Compact Flash interfaces that incorporate a complete set of internal buffers for slot address, data, and control signals. Power control is provided on the SA-1111 Development Module for each socket of the Type II/III dual carriage. The Compact Flash dedicated inner socket requires a PCMCIA-to-Compact Flash adapter board.

Figure 3-3. Audio and External Inputs

#### 3.1.3 Logic Analyzer Connections

Figure 3-4 shows some of the debug features available on the SA-1111 development module. There are four Hewlett-Packard and Tektronix -compatible 38-pin Mictor connectors populated with buffered versions of nearly every signal present on the SA-1110 development board expansion connector for logic analyzer connectivity. See Table 3-1 for a cross reference of these signals in Hewlett-Packard and Tektronix pin assignment schemes. Clocks are available at Mictor connector J21 and J22, supplied as a GPIO output from the SA-1110 Development Board. Header J14 provides two spare buffer inputs available to the user to select additional signals to make present at the logic analyzer through J24. Adapters may be used to connect it to some other brands of logic analyzer connections.

Also shown in Figure 3-4 are the LED latches, U6 and U10, for the bank of 32 SMT green LEDs. These LEDs can be used for development and debug status.

**Table 3-1. Logic Analyzer Pin Assignments**

| Mictor<br>Pin | Tektronix | НР  | J24           | J25          | J21          | J22       |  |  |  |  |  |

|---------------|-----------|-----|---------------|--------------|--------------|-----------|--|--|--|--|--|

| 1             | _         | _   | NC            | NC           | NC           | NC        |  |  |  |  |  |

| 2             | _         | _   | NC            | NC           | NC           | NC        |  |  |  |  |  |

| 3             | CLK       | CLK | NC            | NC           | BSDCLK1      | PROBECLK0 |  |  |  |  |  |

| 4             | 3:7       | D15 | P_SDA         | P_NWE        | BnSDCS_2     | BXD31     |  |  |  |  |  |

| 5             | 3:6       | D14 | P_SCL         | P_NOE        | BXNRAS0      | BXD30     |  |  |  |  |  |

| 6             | 3:5       | D13 | P_GPIO0       | P_RDY        | BXNCAS3      | BXD29     |  |  |  |  |  |

| 7             | 3:4       | D12 | P_GPIO1       | P_NRESET_OUT | BXNCAS2      | BXD28     |  |  |  |  |  |

| 8             | 3:3       | D11 | P_PROBECLK0   | P_RD_NWR     | BXNCAS1      | BXD27     |  |  |  |  |  |

| 9             | 3:2       | D10 | P_TXD2        | P_SDCKE1     | BXNCAS0      | BXD26     |  |  |  |  |  |

| 10            | 3:1       | D9  | P_RXD2        | P_SDCKE0     | BXA25        | BXD25     |  |  |  |  |  |

| 11            | 3:0       | D8  | P_TXD         | P_SDCLK2     | BXA24        | BXD24     |  |  |  |  |  |

| 12            | 2:7       | D7  | P_RXD         | P_SDCLK1     | BXA23        | BXD23     |  |  |  |  |  |

| 13            | 2:6       | D6  | P_BATT_FAULT  | P_SDCLK0     | BXA22        | BXD22     |  |  |  |  |  |

| 14            | 2:5       | D5  | P_GFX_IRQ     | P_NCS5       | BXA21        | BXD21     |  |  |  |  |  |

| 15            | 2:4       | D4  | P_SA1111_PWM1 | P_NCS4       | BXA20        | BXD20     |  |  |  |  |  |

| 16            | 2:3       | D3  | P_SA1111_PWM0 | P_NCS3       | BXA19        | BXD19     |  |  |  |  |  |

| 17            | 2:2       | D2  | P_MSDATA      | P_NCS2       | BXA18        | BXD18     |  |  |  |  |  |

| 18            | 2:1       | D1  | P_MSCLK       | P_NCS1       | BXA17        | BXD17     |  |  |  |  |  |

| 19            | 2:0       | D0  | P_SDATA_OUT   | P_NCS0       | BXA16        | BXD16     |  |  |  |  |  |

| 20            | 0:0       | D0  | P_SDATA_IN    | P_NPREG      | BXA0         | BXD0      |  |  |  |  |  |

| 21            | 0:1       | D1  | P_USB_PLUS    | P_FLASHWAIT  | BXA1         | BXD1      |  |  |  |  |  |

| 22            | 0:2       | D2  | P_USB_MINUS   | P_NIOIS16    | BXA2         | BXD2      |  |  |  |  |  |

| 23            | 0:3       | D3  | P_RXD_SSP     | P_NPWAIT     | BXA3         | BXD3      |  |  |  |  |  |

| 24            | 0:4       | D4  | P_TXD_SSP     | P_SA1111_IRQ | BXA4         | BXD4      |  |  |  |  |  |

| 25            | 0:5       | D5  | P_SFRM        | P_NPCE1      | P_NPCE1 BXA5 |           |  |  |  |  |  |

| 26            | 0:6       | D6  | P_SCLK        | P_NPCE2      | P_NPCE2 BXA6 |           |  |  |  |  |  |

Table 3-1. Logic Analyzer Pin Assignments

| Mictor<br>Pin | Tektronix | НР  | J24             | J25        | J21      | J22      |  |  |  |  |

|---------------|-----------|-----|-----------------|------------|----------|----------|--|--|--|--|

| 27            | 0:7       | D7  | P_USER_PROBE1   | P_NPIOR    | BXA7     | BXD7     |  |  |  |  |

| 28            | 1:0       | D8  | P_USER_PROBE0   | P_NPIOW    | BXA8     | BXD8     |  |  |  |  |

| 29            | 1:1       | D9  | P_SMROM_EN      | P_NPWE     | BXA9     | BXD9     |  |  |  |  |

| 30            | 1:2       | D10 | P_XCVR2OE       | P_NPOE     | BXA10    | BXD10    |  |  |  |  |

| 31            | 1:3       | D11 | P_NRESET_IN     | P_BGPIO_27 | BXA11    | BXD11    |  |  |  |  |

| 32            | 1:4       | D12 | P_INGFXRESET    | P_MBGNT    | BXA12    | BXD12    |  |  |  |  |

| 33            | 1:5       | D13 | P_AUDIO_CLK_OUT | P_MBREQ    | BXA13    | BXD13    |  |  |  |  |

| 34            | 1:6       | D14 | P_BIT_CLK       | P_XNSDRAS  | BXA14    | BXD14    |  |  |  |  |

| 35            | 1:7       | D15 | P_FRAME_SYNC    | P_XNSDCAS  | BXA15    | BXD15    |  |  |  |  |

| 36            | CLK       | CLK | NC              | NC         | BXNSDRAS | BXNSDCAS |  |  |  |  |

| 37            | _         | _   | NC              | NC         | NC       | NC       |  |  |  |  |

| 38            | _         | _   | NC              | NC         | NC       | NC       |  |  |  |  |

| 39            | GND       | GND | GND             | GND        | GND      | GND      |  |  |  |  |

| 40            | GND       | GND | GND             | GND        | GND      | GND      |  |  |  |  |

| 41            | GND       | GND | GND             | GND        | GND      | GND      |  |  |  |  |

| 42            | GND       | GND | GND             | GND        | GND      | GND      |  |  |  |  |

| 43            | GND       | GND | GND             | GND        | GND      |          |  |  |  |  |

Figure 3-4. Debug and LED Connections

#### 4.1 General-Purpose Expansion Bus Headers

The general-purpose expansion bus headers provided on the SA-1110 Development Board are referred to as the Xbus headers (not to be confused with ISA Xbus). All SA-1110 address, data and memory interface signals are buffered before driving the Xbus headers.

The Xbus headers allow interfacing to the SA-1111 Development Module as well as a third-party graphics chips.

For information on the system memory map, see the *Intel*<sup>®</sup> *StrongARM*<sup>®</sup> *SA-1110 Development Board User's Guide*.

#### 4.2 Expansion Flash Memory

Two socketed Intel page mode 32Mbyte StrataFlash™ devices provide expansion flash and a selectable boot flash. The SA-1111 Development Module's flash bank is populated with 32Mbyte socketed Intel fast page mode 3V StrataFlash devices. These components provide 32 Mbyte flash banks. The design supports 56-lead TSOP StrataFlash FlashFile™ devices with densities of 32 Mbit, 64 Mbit, and 128 Mbit.

The SA-1110 microprocessor always boots from Bank 0. Bank 0, which can be on the SA-1110 Development Board or the SA-1111 Development Module, is controlled by component SW2, switch 8 when the SA-1111 Development Module is assembled to the SA-1110 motherboard. When Bank 0 is on the SA-1110 Development Board, Bank 1 is on the SA-1111 Development Module. When Bank 0 is on the SA-1111 Development Module, Bank 1 is on the SA-1110 Development Board does not have a daughterboard attached, Bank 0 is on the SA-1110 Development Board.

The control of the location of Bank 0 is described in Table 4-1.

#### Table 4-1. Bank 0 Location

| When Component SW2 Switch 8 is | Then Bank 0 is located on the: |

|--------------------------------|--------------------------------|

| ON position                    | SA-1110 Development Board      |

| OFF position                   | SA-1111 Development Module     |

The SA-1111 Development Module circuitry that controls the location of Bank 0 is shown in the SA-1111 schematics on sheet 7 of 11, signal name SWPK7. When this signal enters the SA-1110 Development Board, it becomes SWAP FLASH.

# 4.3 General-purpose Status Input Switch and Jumper Descriptions

Component SW2 is used for determining where bank 0 is located, and jumps to one of four boot images. Unused switches are user defined.

The switch setting may be read from the Switch Status Register in the CPLD SWPK register.

Table 4-2. Switch and Jumper Descriptions

| Switch | Condition            | Function                                                                                                          | Default              |  |  |  |  |  |  |

|--------|----------------------|-------------------------------------------------------------------------------------------------------------------|----------------------|--|--|--|--|--|--|

| SW2-1  | LSB of 2 bit address | GPIO 0 –part of a 2 bit address to jump to one of four boot images.                                               | Off                  |  |  |  |  |  |  |

| SW2-2  | MSB of 2 bit address | GPIO 1-part of a 2 bit address to jump to one of four boot images.                                                | Off                  |  |  |  |  |  |  |

| SW2-3  | _                    | User defined                                                                                                      | Off                  |  |  |  |  |  |  |

| SW2-4  | _                    | User defined                                                                                                      | Off                  |  |  |  |  |  |  |

| SW2-5  | _                    | User defined                                                                                                      | Off                  |  |  |  |  |  |  |

| SW2-6  | _                    | User defined                                                                                                      | Off                  |  |  |  |  |  |  |

| SW2-7  | _                    | User defined                                                                                                      | Off                  |  |  |  |  |  |  |

| SW2-8  | _                    | Off — Bank 0 is located on the SA-1111 Development Module On — Bank 0 is located on the SA-1110 Development Board | On                   |  |  |  |  |  |  |

| SW1-1  | _                    | Ethernet Controller – ECEEP                                                                                       | Off                  |  |  |  |  |  |  |

| SW1-2  | _                    | Ethernet Controller – IOS2                                                                                        | Off                  |  |  |  |  |  |  |

| SW1-3  | _                    | Ethernet Controller – IOS1                                                                                        | Off                  |  |  |  |  |  |  |

| SW1-4  | _                    | Ethernet Controller – IOS0                                                                                        | Off                  |  |  |  |  |  |  |

| J26    | Clock<br>selection   | SA-1111 SDRAM Bank Select                                                                                         | Connect pins 2 and 3 |  |  |  |  |  |  |

#### 4.4 CPLD Register Map

The SA-1111 Development Module implements several memory mapped IO registers. The SA-1110 CS2 address space, which starts at 0x1000,0000, is dedicated to system level registers. The SA-1111 Development Module registers are implemented in a CPLD with an 8-bit data path to the 32-bit system bus. The 8-bit CPLD is addressed on 32-bit word boundaries. The CPLD needs lower address bits A[7:2] to decode the registers within the CS2 address space.

The SA-1111 device should be used for controlling the interface to different features. For example, use the SA-1111 to control the audio controls, do **not** use the CPLD to control the audio controls.

The General-Purpose I/O (GPIO) interface is a functional block that provides up to 19 bits of programmable input/output. As inputs, each pin can be configured as an interrupt source, wake-up source, or both. The GPIO ports provide general-purpose digital I/O capabilities for the SA-1111 (see sheet 9 of 11).

In addition, several register based GPIO pins are assigned to sense and control the CF socket. The SA-1110 GPIO22 and GPIO21 pins serve dual functions in the SA-1110 CF design. When the SA-1111 Development Module is attached, GPIO22 and GPIO21 are configured to be the GPIO alternate function bus DMA control signals nMBREQ and nMBGNT. When the SA-1111 Development Module is not attached and the SA-1110 CF slot is active, GPIO22 and GPIO21 are used as CF card detect interrupt and CF RDY interrupt signals.

For more information about GPIOs, see the *Intel*<sup>®</sup> *StrongARM*<sup>®</sup> *SA-1111 CPU Companion Chip Developer's Manual.*

Table 4-3 describes the SA-1111 CPLD register map, which controls the CPU transceivers and some of the CF support signals.

For more information about CPLD functions, see Appendix 4.11.

The CPLD source code for the SA-1111 Development Module is provided in Appendix A.

**Table 4-3. Register Descriptions**

| Address   | Name                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Description                    |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------|

| 1000,00C0 | AUD CTL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Audio controls TBD             |

| 1000,0000 | AOD_CTL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | CPLD [TBD] (RW)                |

| 1000,00B0 | MDM_CTL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Modem control signals          |

| 1000,0000 | WDW_OTE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | CPLD [TBD] (RW)                |

| 1000,00A0 | CR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Control Register               |

| 1000,0070 | J GIK                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | CPLD [7:0] (RW)                |

| 1000,0090 | KP X OUT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Keypad row write               |

| 1000,0000 | \(\( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( | CPLD [4:0] (RW)                |

| 1000,0080 | KP Y IN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Keypad column read             |

| 1000,0000 | 100 = 1 = 114                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | CPLD [3:0] (RO)                |

| 1000,0020 | SWPK                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Switch pack, 8 switches        |

| 1000,0020 | OWIK                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | CPLD [7:0] (RO)                |

|           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | System ID register             |